# Within-Camera Multilayer Perceptron DVS Denoising OPR June 18, 2023 EVNTVIS

Antonio Rios-Navarro<sup>2,1</sup>, Shasha Guo<sup>3,1</sup>, (Aba) G. Abarajithan<sup>5</sup>, (Vijay) K. Vijayakumar<sup>5</sup>, Alejandro Linares-Barranco<sup>2</sup>, Thea Aarrestad<sup>4</sup>, Ryan Kastner<sup>5,1</sup>, and Tobi Delbruck<sup>1</sup> <sup>1</sup> Sensors Group, Institute of Neuroinformatics, Univ. of Zurich and ETH Zurich, Switzerland, <sup>2</sup> Robotic and Tech of Computers Group, SCORE lab, ETSI-EPS, Univ. of Seville, Spain <sup>3</sup> College of Electronic Engineering, National University of Defense Technology (NUDT), China, <sup>4</sup> Inst. of Particle Physics, ETH Zurich, Switzerland, <sup>5</sup> Univ. of California, San Diego, USA

and Prof. Shih-Chii Liu (INI), Prof. Mingu Kang (UCSD), and anonymous reviewers for their support and suggestions to improve the paper.

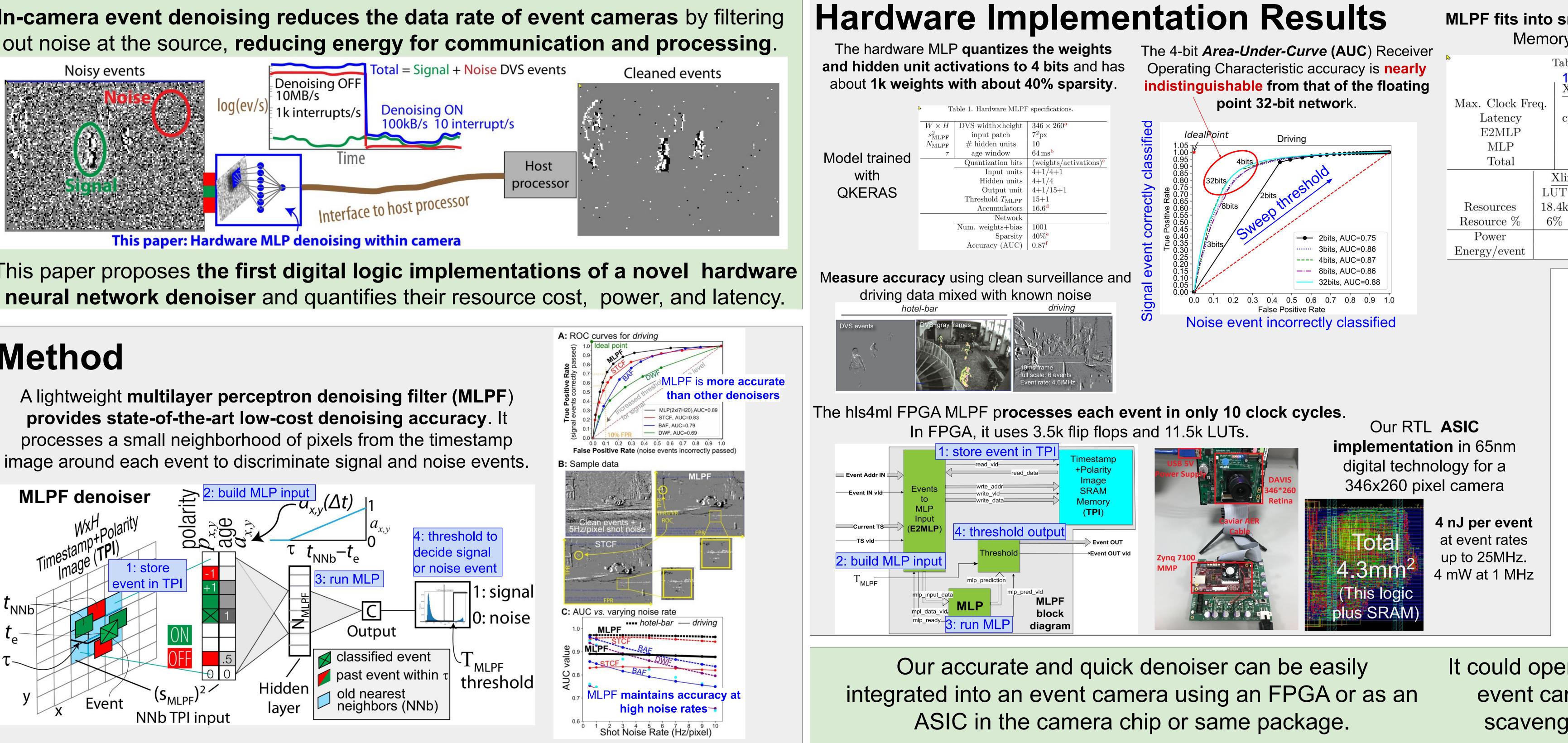

It could open new areas of always-on event camera application under scavenged and battery power.

MLPF fits into small FPGA or small ASIC area and has 40 ns latency. Memory for the 2D timestamp image dominates cost.

| ble 2. FOI                     | As of the ha             | rdware N                     | ILPFs f                      | or Table 1 p                    | arameters.                                           |                                 |  |

|--------------------------------|--------------------------|------------------------------|------------------------------|---------------------------------|------------------------------------------------------|---------------------------------|--|

| <b> 2 y old  </b><br>Xlinx Zyn | <b>⁼PGA</b><br>q XC7Z100 | <mark>Mode</mark><br>  Xlinx | rn <mark>\$40</mark><br>Zynq | <mark>0 FPGA</mark><br>U+ ZU3CG | Cheap digital process<br><u>65nm ASIC. Vdd=1.08V</u> |                                 |  |

| 100                            | MHz                      |                              | 236 l                        | MHz                             | $833\mathrm{MHz}$                                    |                                 |  |

| eycles                         | ns                       | cycles                       | S                            | ns                              | cycles 1                                             | les ns                          |  |

| 7                              | 70                       | 7                            |                              | $\sim 30$                       | 30 3                                                 | 36                              |  |

| 3                              | 30                       | 3                            |                              | $\sim \! 13$                    | 3 3                                                  | 3.6                             |  |

| 10                             | 100                      | 10                           |                              | $\sim \!\! 43$                  | 33 4                                                 | 40                              |  |

| inx Zynq xc7z100               |                          | Xlinx 2                      | Zynq U                       | + ZU3CG                         | <u>65nm ASIC</u>                                     |                                 |  |

| ' FF                           | BRAM                     | LUT                          | $\mathbf{FF}$                | BRAM                            | Logic area                                           | SRAM area                       |  |

| x 3.9k                         | $400^{\mathbf{a}}$       | 24.6k                        | 3.8k                         | $400^{\mathbf{a}}$              | 0.022mm <sup>2</sup>                                 | $4.3^{\mathrm{b}}\mathrm{mm}^2$ |  |

| 0.72%                          | 26%                      | 34%                          | 2%                           | 92%                             | _                                                    | -                               |  |

|                                | Not re                   | elevant                      | 40mW <sup>c</sup>            |                                 |                                                      |                                 |  |

|                                | Not re                   | elevant                      | $4nJ^{d}$                    |                                 |                                                      |                                 |  |

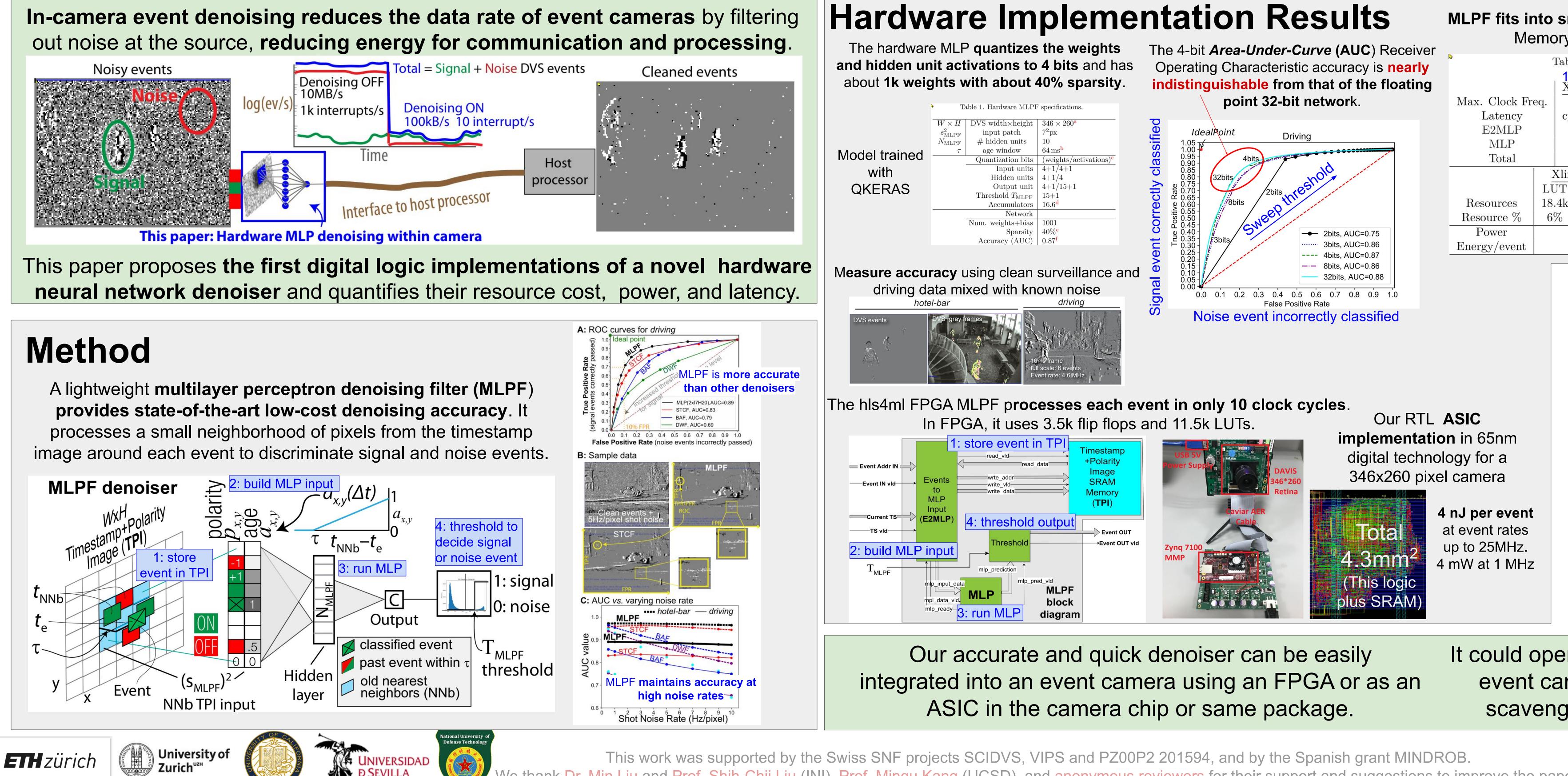

## **Comparison with SOA**

Hardware denoisers generally seek to minimize memory, which leads to poor discrimination accuracy at high noise rates. The MLPF has by far the best AUC accuracy. Its maximum denoising rate of 25 MHz is suitable for recent event cameras.

| Denoiser      | hotel-bar<br>AUC <sup>a</sup> | driving<br>AUC <sup>a</sup> | $\mathrm{Mem}(\#)^{\mathrm{b}}$ | Max. Ever<br>Rate <sup>c</sup><br>MHz |

|---------------|-------------------------------|-----------------------------|---------------------------------|---------------------------------------|

| MLPF FPGA     | 0.96                          | 0.87                        | $W \times H$                    | 23                                    |

| MLPF ASIC     | "                             | "                           | $W \times H$                    | 25                                    |

| BAF [17]      | 0.89                          | 0.79                        | $W \times H$                    | 3.6                                   |

| ONF [16]      | $0.01^{\mathrm{e}}$           | $0.01^{\rm e}$              | $2 \times (W + H)$              | 3                                     |

| HashHeat [18] | 0.67                          | $0.56^{\mathrm{f}}$         | 128                             | 100                                   |

| IIRs [19]     | NA                            | NA                          | $W\times H^{\rm g}$             | 385                                   |

| LDSI [20]     | NA                            | NA                          | $W \times H$                    | $3?^{\mathrm{d}}$                     |

https://github.com/SensorsINI/dnd hls